Готовые презентации на тему:

- Образование

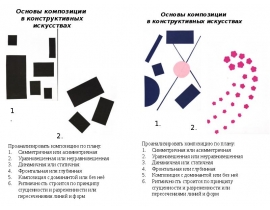

- Искусство и Фото

- Наши презентации

- Авто/мото

- Технологии

- Бизнес и предпринимательство

- Карьера

- Данные и аналитика

- Дизайн

- Устройства и комплектующие

- Экономика и Финансы

- Машиностроение

- Развлечения и Юмор

- Путешествия

- Eда

- Политика

- Юриспруденция

- Здоровье и Медицина

- Интернет

- Инвестиции

- Закон

- Стиль жизни

- Маркетинг

- Мобильные технологии

- Новости

- Недвижимость

- Рекрутинг

- Розничная торговля

- Таможня, ВЭД, Логистика

- Наука

- Услуги

- Программное обеспечение

- Спорт

- Музыка

- Шаблоны презентации

- Детские презентации

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- История

- Литература

- Информатика

- Математика

- Обществознание

- Русский язык

- Физика

- Философия

- Химия

- МХК

- ОБЖ

- Окружающий мир

- Педагогика

- Технология

- Начальная школа

- Раскраски для детей

- Товароведение

- Менеджмент

- Страхование

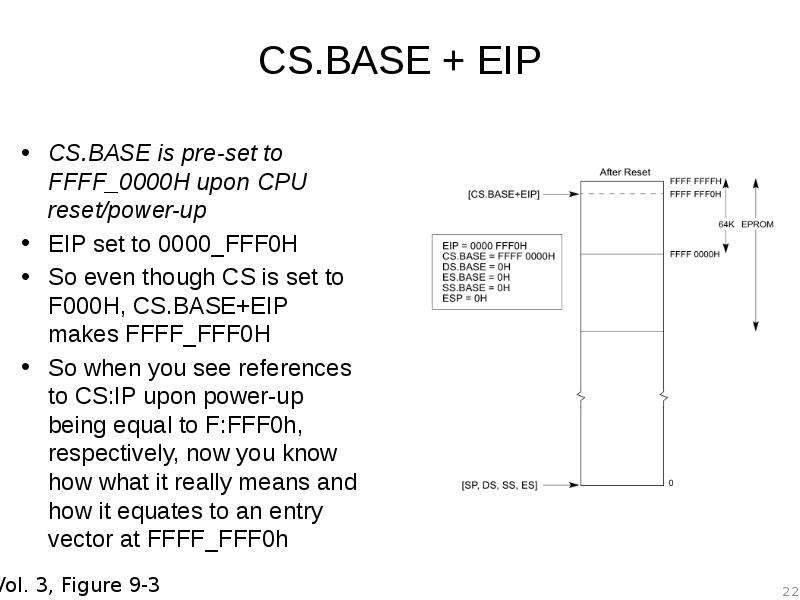

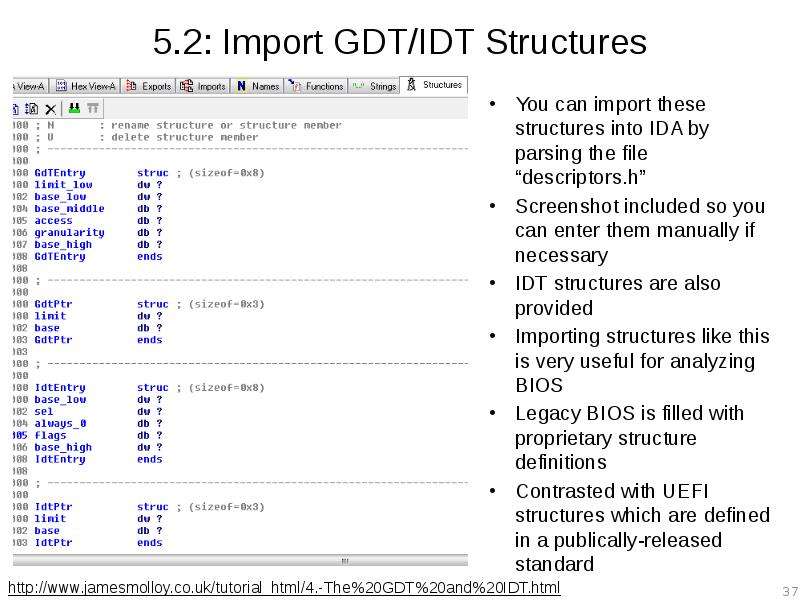

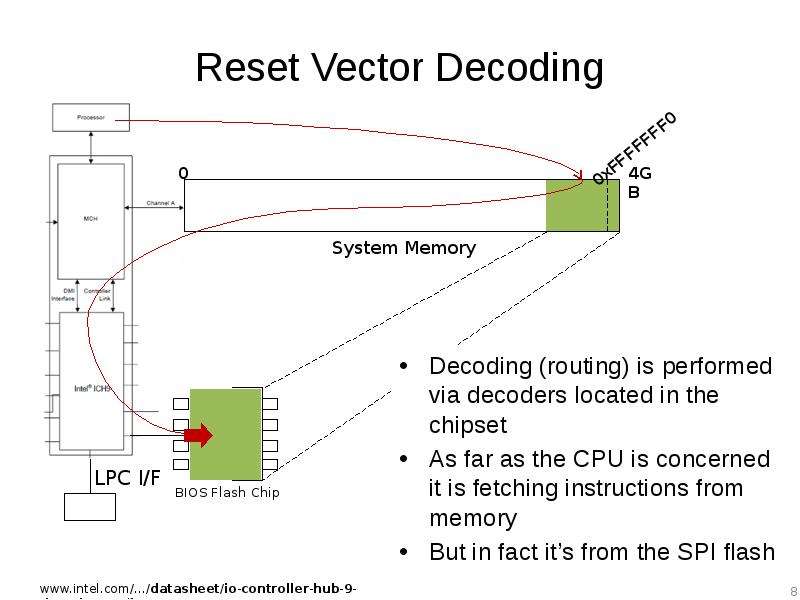

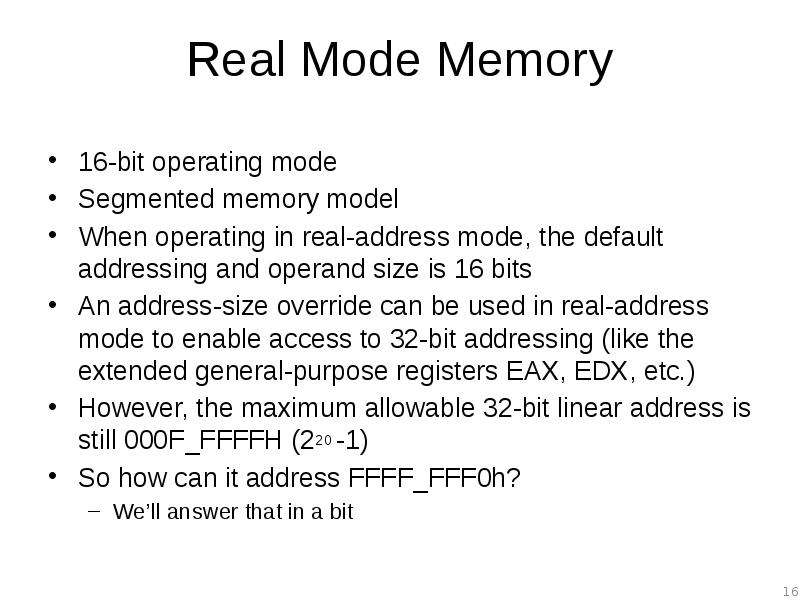

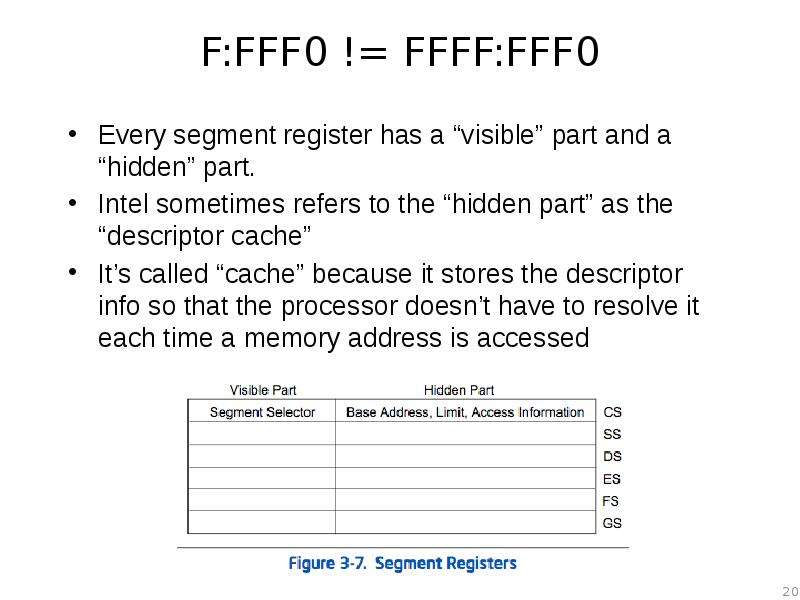

![Descriptor Cache

“When a segment selector is loaded into the visible part of a segment register, the processor also loads the hidden part of the segment register with the base address, segment limit, and [access information] from the segment descriptor pointed to by the segment selector.”

Real Mode doesn’t have protected mode style access-control so the [access information] part is ignored

This means that the hidden part isn’t modified until after a value is loaded into the segment selector

So the moment CS is modified, the CS.BASE of FFFF_0000H is replaced with the new value of CS (left shifted 4 bits)](/documents_6/76ca5a9609ab0f30d045493ce55a47e0/img20.jpg)