Готовые презентации на тему:

- Образование

- Искусство и Фото

- Наши презентации

- Авто/мото

- Технологии

- Бизнес и предпринимательство

- Карьера

- Данные и аналитика

- Дизайн

- Устройства и комплектующие

- Экономика и Финансы

- Машиностроение

- Развлечения и Юмор

- Путешествия

- Eда

- Политика

- Юриспруденция

- Здоровье и Медицина

- Интернет

- Инвестиции

- Закон

- Стиль жизни

- Маркетинг

- Мобильные технологии

- Новости

- Недвижимость

- Рекрутинг

- Розничная торговля

- Таможня, ВЭД, Логистика

- Наука

- Услуги

- Программное обеспечение

- Спорт

- Музыка

- Шаблоны презентации

- Детские презентации

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- История

- Литература

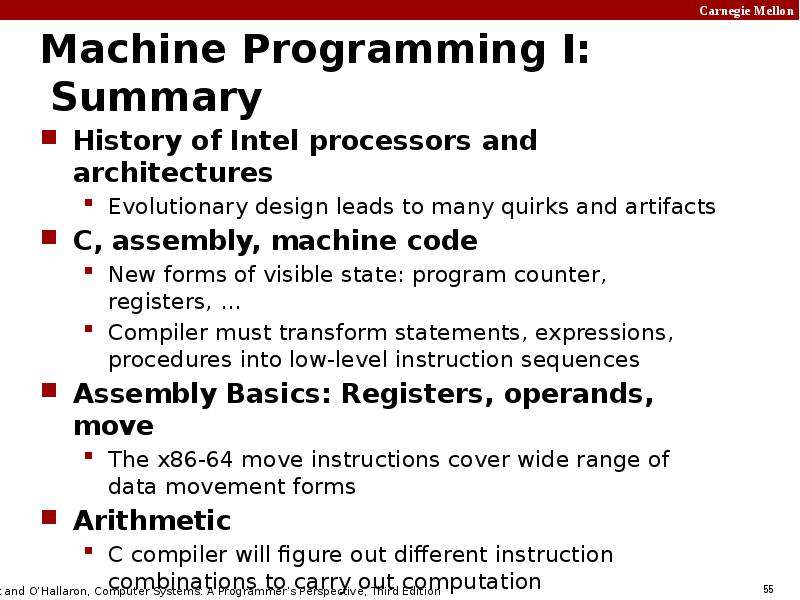

- Информатика

- Математика

- Обществознание

- Русский язык

- Физика

- Философия

- Химия

- МХК

- ОБЖ

- Окружающий мир

- Педагогика

- Технология

- Начальная школа

- Раскраски для детей

- Товароведение

- Менеджмент

- Страхование

![Simple Memory Addressing Modes

Normal (R) Mem[Reg[R]]

Register R specifies memory address

Aha! Pointer dereferencing in C

movq (%rcx),%rax

Displacement D(R) Mem[Reg[R]+D]

Register R specifies start of memory region

Constant displacement D specifies offset

movq 8(%rbp),%rdx](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img21.jpg)

![Simple Memory Addressing Modes

Normal (R) Mem[Reg[R]]

Register R specifies memory address

Aha! Pointer dereferencing in C

movq (%rcx),%rax

Displacement D(R) Mem[Reg[R]+D]

Register R specifies start of memory region

Constant displacement D specifies offset

movq 8(%rbp),%rdx](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img30.jpg)

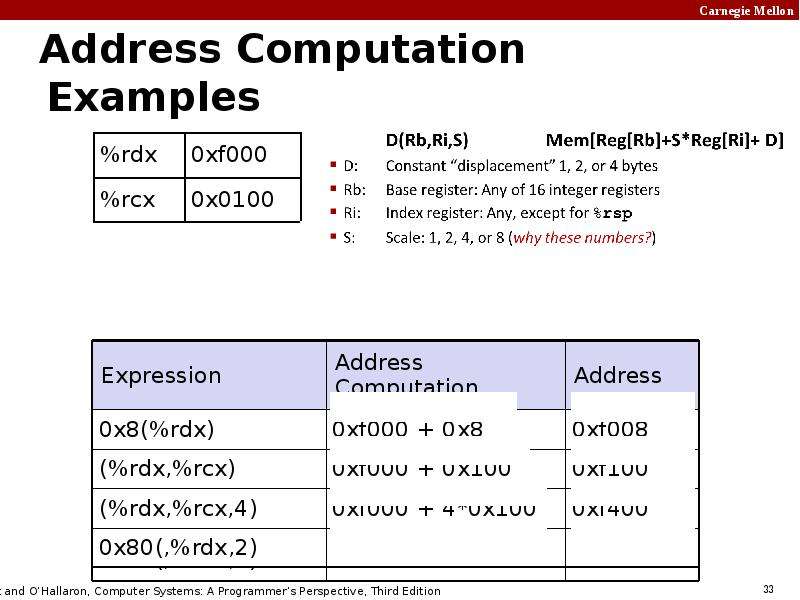

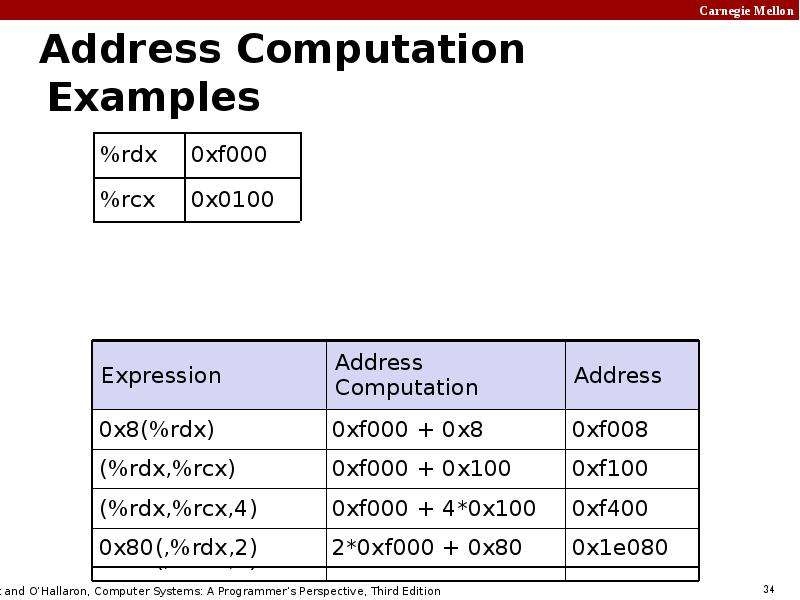

![Complete Memory Addressing Modes

Most General Form

D(Rb,Ri,S) Mem[Reg[Rb]+S*Reg[Ri]+ D]

D: Constant “displacement” 1, 2, or 4 bytes

Rb: Base register: Any of 16 integer registers

Ri: Index register: Any, except for %rsp

S: Scale: 1, 2, 4, or 8 (why these numbers?)

Special Cases

(Rb,Ri) Mem[Reg[Rb]+Reg[Ri]]

D(Rb,Ri) Mem[Reg[Rb]+Reg[Ri]+D]

(Rb,Ri,S) Mem[Reg[Rb]+S*Reg[Ri]]](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img31.jpg)

![Address Computation Instruction

leaq Src, Dst

Src is address mode expression

Set Dst to address denoted by expression

Uses

Computing addresses without a memory reference

E.g., translation of p = &x[i];

Computing arithmetic expressions of the form x + k*y

k = 1, 2, 4, or 8

Example](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img35.jpg)

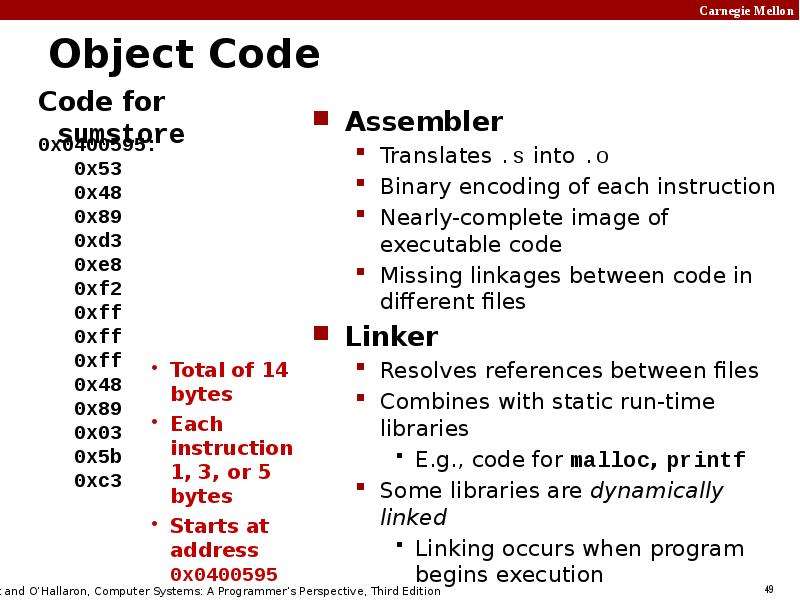

![Turning C into Object Code

Code in files p1.c p2.c

Compile with command: gcc –Og p1.c p2.c -o p

Use basic optimizations (-Og) [New to recent versions of GCC]

Put resulting binary in file p](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img42.jpg)

![Machine Instruction Example

C Code

Store value t where designated by dest

Assembly

Move 8-byte value to memory

Quad words in x86-64 parlance

Operands:

t: Register %rax

dest: Register %rbx

*dest: Memory M[%rbx]

Object Code

3-byte instruction

Stored at address 0x40059e](/documents_6/eeb844c7d4a4969ed9f35ab1ed76effa/img49.jpg)