Описание слайда:

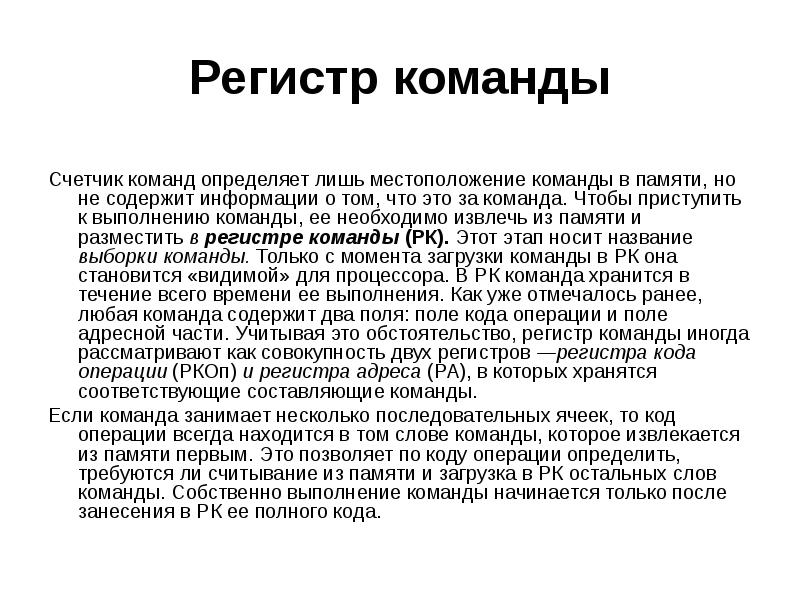

Счетчик команд (СК) — неотъемлемый элемент устройства управления любой ВМ, построенной в соответствии с фон-неймановским принципом программного управления. Согласно этому принципу соседние команды программы располагаются в ячейках памяти со следующими по порядку адресами и выполняются преимущественно в той же очередности, в какой они размещены в памяти ВМ. Таким образом, адрес очередной команды может быть получен путем увеличения адреса ячейки, из которой была считана текущая команда, на длину выполняемой команды, представленную числом занимаемых ею ячеек. Реализацию такого режима и призван обеспечивать счетчик команд — двоичный счетчик, в котором хранится и модифицируется адрес очередной команды программы. Перед началом вычислений в СК заносится адрес ячейки основной памяти, где хранится команда, которая должна быть выполнена первой. В процессе выполнения каждой команды путем увеличения содержимого СК на длину выполняемой команды в счетчике формируется адрес следующей подлежащей выполнению команды. В рассматриваемой ВМ любая команда занимает одну ячейку, поэтому содержимое СК увеличивается на единицу, что обеспечивается подачей сигнала управления +1СК. По завершении текущей команды адрес следующей команды программы всегда берется из счетчика команд. Для изменения естественного порядка вычислений (перехода в иную точку программы) достаточно занести в СК адрес точки перехода.

Счетчик команд (СК) — неотъемлемый элемент устройства управления любой ВМ, построенной в соответствии с фон-неймановским принципом программного управления. Согласно этому принципу соседние команды программы располагаются в ячейках памяти со следующими по порядку адресами и выполняются преимущественно в той же очередности, в какой они размещены в памяти ВМ. Таким образом, адрес очередной команды может быть получен путем увеличения адреса ячейки, из которой была считана текущая команда, на длину выполняемой команды, представленную числом занимаемых ею ячеек. Реализацию такого режима и призван обеспечивать счетчик команд — двоичный счетчик, в котором хранится и модифицируется адрес очередной команды программы. Перед началом вычислений в СК заносится адрес ячейки основной памяти, где хранится команда, которая должна быть выполнена первой. В процессе выполнения каждой команды путем увеличения содержимого СК на длину выполняемой команды в счетчике формируется адрес следующей подлежащей выполнению команды. В рассматриваемой ВМ любая команда занимает одну ячейку, поэтому содержимое СК увеличивается на единицу, что обеспечивается подачей сигнала управления +1СК. По завершении текущей команды адрес следующей команды программы всегда берется из счетчика команд. Для изменения естественного порядка вычислений (перехода в иную точку программы) достаточно занести в СК адрес точки перехода.

Разработчики ВМ используют иные названия, в частности программный счетчик (PC, Program Counter) или указатель команды (IP, Instruction Pointer). Последнее определение представляется наиболее удачным, поскольку точнее отражает назначение рассматриваемого узла УУ.