Описание слайда:

По состоянию полей адреса и условий перехода текущей микрокоманды, а также по значению сигналов логических условий, выдаваемых операционным автоматом, в блоке микропрограммного управления формируется адрес ячейки памяти, в которой хранится следующая микрокоманда исполняемой микропрограммы. В следующем тактовом периоде микрокоманда считывается из управляющей памяти. Разряды поля управляющих сигналов поступают в операционный автомат, который выполняет данную микрокоманду Vk, а разряды поля адреса и поля условий перехода — в блок микропрограммного управления, который формирует адрес очередной микрокоманды. Процесс продолжается до тех пор, пока не будет выполнена вся микропрограмма. Так как структура управляющего автомата стандартна, основные усилия разработчика направлены на составление микропрограммы, которая записывается в ячейки постоянного запоминающего устройства.

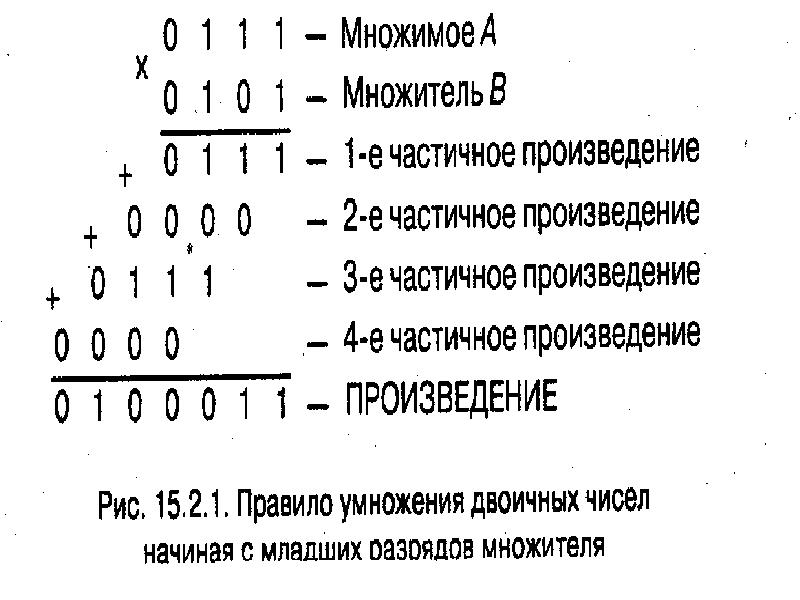

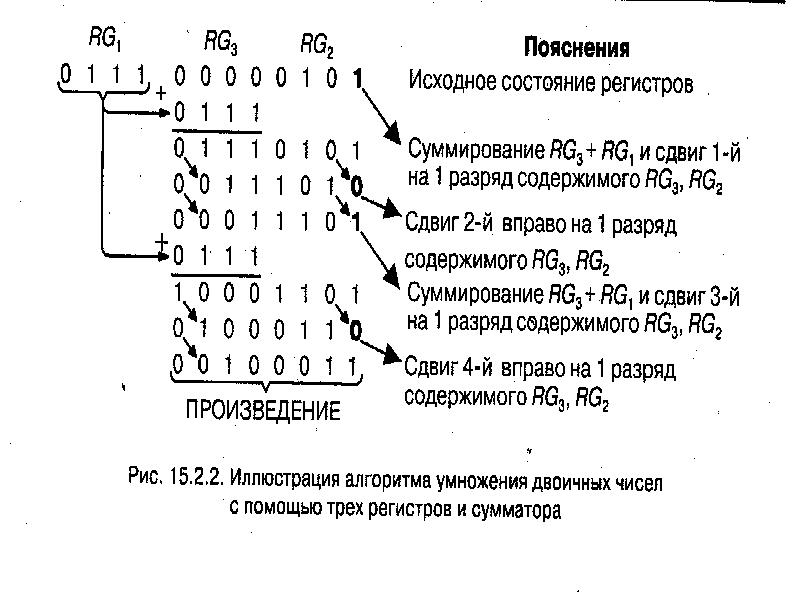

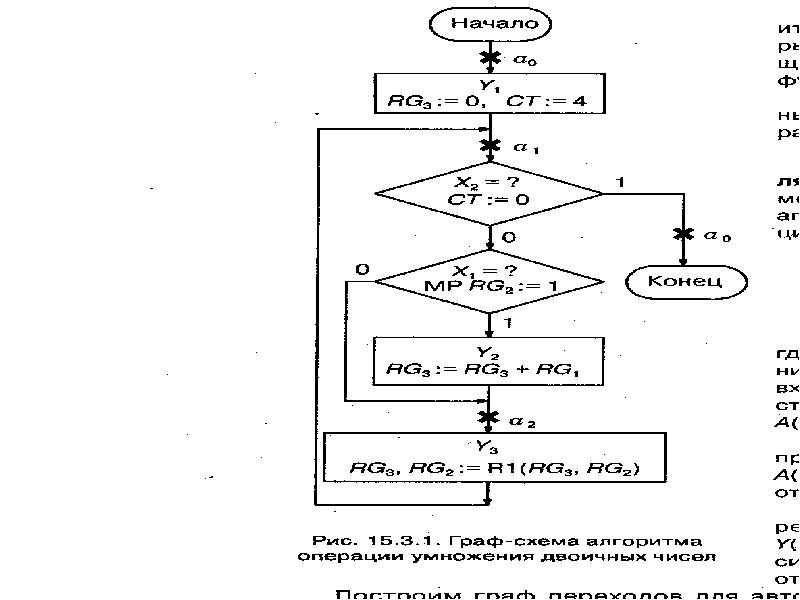

Составим микропрограмму для выполнения операции умножения двоичных чисел по рассмотренному выше алгоритму, представленному на рис. 15.3.1.

Выбор формата и числа разрядов микрокоманды. Как отмечено выше, в формате микрокоманды микропрограммы должно быть предусмотрено поле адреса, которое содержит код адреса следующей микрокоманды. Выберем число разрядов кода адреса равным трем, что позволит хранить в управляющей памяти адреса восьми микрокоманд. Если выполнение микрокоманд не связано с логическими условиями, то адресный код/42/4,/40 передается через блок микропрограммного управления в управляющую память без изменения. При наличии условного перехода адрес в блоке микропрограммного управления модифицируется. По этой причине в формате микрокоманды предусмотрено поле условий переходов, содержащее три разряда Π, ΠΧ2, /7Х,. Значение /7 = 0 соответствует безусловному переходу. В этом случае разряды /7Х2, ПX^ микрокоманды микропрограммы могут принимать любые значения (0 или 1). Значение П= 1 инициирует проверку логических условий Х2 или X,. При проверке логического условия Х2 необходимо установить ПХ2 = 1, ЛХ, = 0; при проверке логического условия X, — ЛХ2 = О, ЛХ, = 1. Следует отметить, что сигналы Х2, X, логических условий формирует операционный автомат, а разряды Π, ЛХ2, ЛХ, проверки логических условий содержатся в микрокомандах микропрограммы, которая хранится в управляющей памяти (рис. 15.4.1). В поле управляющих сигналов заносятся значения микрокоманд У,, У2, У3 или сигналов у,, у2, уэ, у4, у5, активизирующих выполнение микроопераций. В табл. 15.4.1 приведен выбранный формат микрокоманды микропрограммы.

Таблица 15.4.1

Формат микрокоманды микропрограммы

Поле адреса

Поле условий перехода

Поле управляющих сигналов

\

Λ

*0

Π

пхг

ЛХ,

У5

У4

У

у

У,

Разметка граф-схемы алгоритма. Каждой вершине граф-схемы алгоритма (рис. 15.3.1) операции умножения двоичных чисел за исключением начальной поставим в соответствие микрокоманду микропрограммы. Микрокоманды МК1, МК2, МКЗ, ... микропрограммы будем хранить в ячейках управляющей памяти с адресами 000, 001, 010, ... соответственно. Для обращения к ячейкам'воспользуемся естественной адресацией, при которой различают микрокоманды двух типов: операционные и управляющие. Тип микрокоманды зависит от значения одноразрядного поля признака П: значению П = 0 соответствует операционная