Готовые презентации на тему:

- Образование

- Искусство и Фото

- Наши презентации

- Авто/мото

- Технологии

- Бизнес и предпринимательство

- Карьера

- Данные и аналитика

- Дизайн

- Устройства и комплектующие

- Экономика и Финансы

- Машиностроение

- Развлечения и Юмор

- Путешествия

- Eда

- Политика

- Юриспруденция

- Здоровье и Медицина

- Интернет

- Инвестиции

- Закон

- Стиль жизни

- Маркетинг

- Мобильные технологии

- Новости

- Недвижимость

- Рекрутинг

- Розничная торговля

- Таможня, ВЭД, Логистика

- Наука

- Услуги

- Программное обеспечение

- Спорт

- Музыка

- Шаблоны презентации

- Детские презентации

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- История

- Литература

- Информатика

- Математика

- Обществознание

- Русский язык

- Физика

- Философия

- Химия

- МХК

- ОБЖ

- Окружающий мир

- Педагогика

- Технология

- Начальная школа

- Раскраски для детей

- Товароведение

- Менеджмент

- Страхование

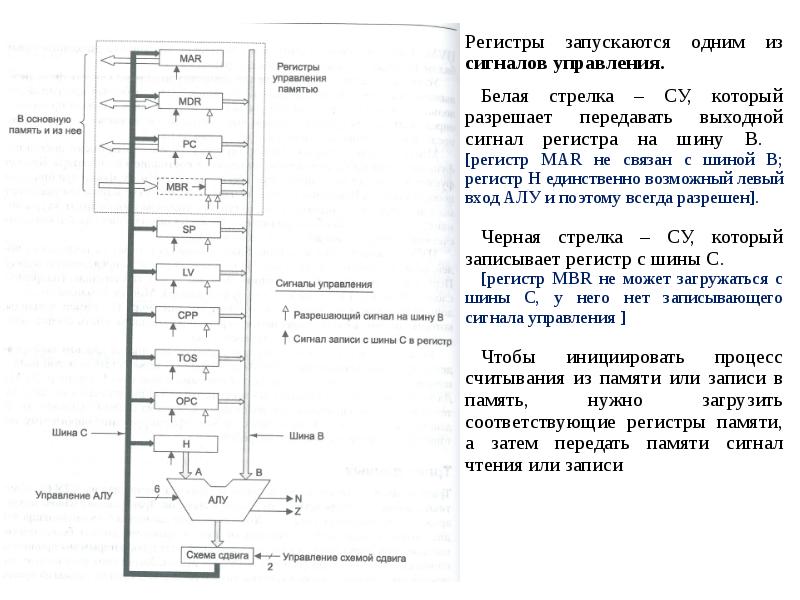

![Уровень микроархитектуры

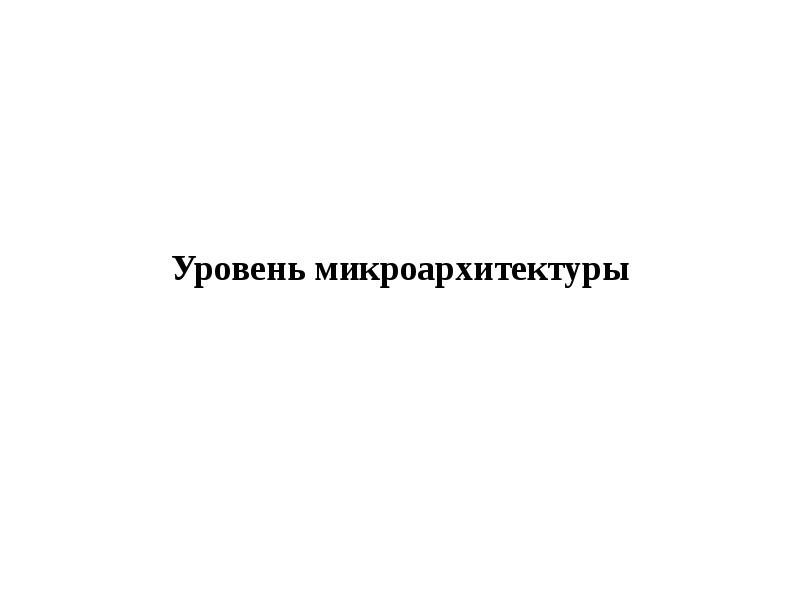

Задача – интерпретация команд уровня архитектуры команд.

Строение уровня микроархитектуры зависит от того каков уровень архитектуры команд, а также от стоимости и назначения компьютера:

RISC машины: на уровне архитектуры команд обычно находятся простые команды которые выполняются за один цикл

Core i7: на этом уровне имеются более сложные команды; выполнение одной такой команды занимает несколько циклов

[Чтобы выполнить команду, нужно найти операнды в памяти, считать их и записать полученные результаты обратно в память]](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img2.jpg)

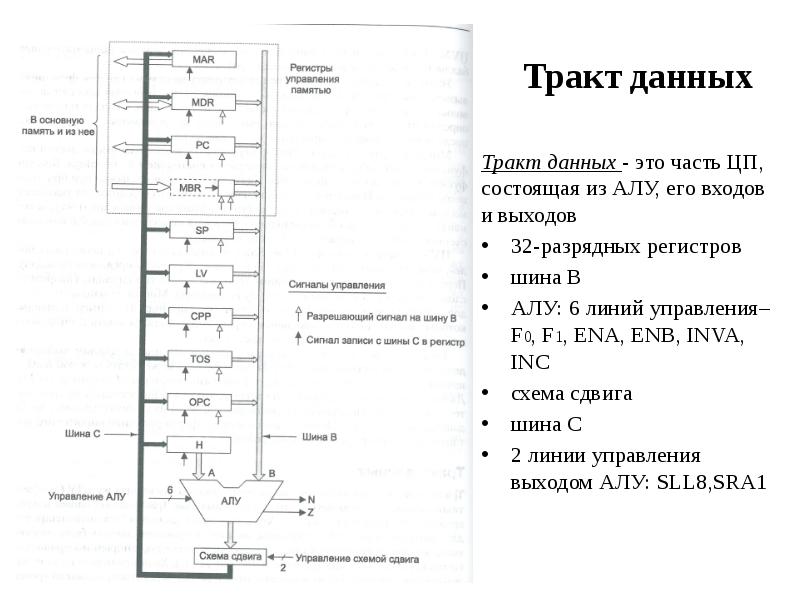

![Тракт данных

Содержание большинства регистров передается на шину В.

Выходной сигнал АЛУ управляет схемой сдвига и далее шиной С.

Значение с шины С может записываться в один или несколько регистров одновременно.

Шину А мы введем позже, а пока представим, что ее нет.

Функционирование АЛУ зависит от линий управления. [Перечеркнутая стрелочка с цифрой 6 сверху указывает на наличие шести линии управления АЛУ:

F0 и F1 служат для задания операции;

ENA и ENB – для разрешения входных сигналов А и В соответственно;

INVA – для инверсии левого входа ;

INC – для переноса бита в младший разряд прибавление 1 к результату.]](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img6.jpg)

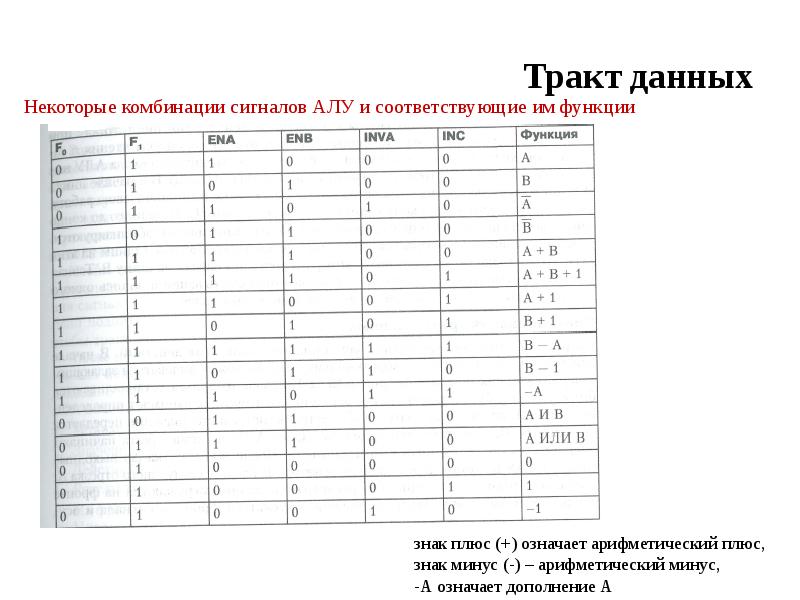

![Тракт данных

АЛУ содержит два входа для данных:

левый вход (А) [c левым входом связан регистр временного хранения Н]

правый вход (В) [c правым входом связана шина В, на которую могут поступать значения с одного из девяти источников (серые стрелочки)].

В регистр Н может поступать функция АЛУ, которая проходит через правый вход (из шины В) к выходу АЛУ. Одна из таких функций — сложение входных сигналов АЛУ: сигнал ENA отрицателен и левый вход получает значение 0. Если к значению шины В прибавить 0, это значение не изменится. Затем результат проходит через схему сдвига (также без изменений) и сохраняется в регистре Н.

Линии управления SLL8 и SRA1

используются независимо от остальных.

служат для управления выходом АЛУ.

Линия SLL8 (Shift Left Logical — логический сдвиг влево) сдвигает число влево на 1 байт, заполняя 8 самых младших двоичных разрядов нулями. Линия SRA1 (Shift Right Arithmetic — арифметический сдвиг вправо) сдвигает число вправо на 1 бит, оставляя самый старший двоичный без изменений](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img7.jpg)

![Тракт данных

Операции чтения и записи регистра могут выполняться за один цикл:

Пример: значение SP поместить на шину В, закрыть левый вход АЛУ, установить сигнал INC и сохранить полученный результат в регистре SP увеличив т.о. его значение на 1

Процессы чтения и записи происходят в разных частях цикла:

Когда в качестве правого входа АЛУ выбирается один из регистров, его значение помещается на шину В в начале цикла и хранится там на протяжении всего цикла.

Затем АЛУ выполняет свою работу результат которой через схему сдвига поступает на шину С.

Незадолго до конца цикла, когда значения выходных сигналов АЛУ и схемы сдвига стабилизируются, содержание шины С передается в один или несколько регистров. [Одним из этих регистров вполне может быть тот, с которого поступил сигнал на шину В].](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img8.jpg)

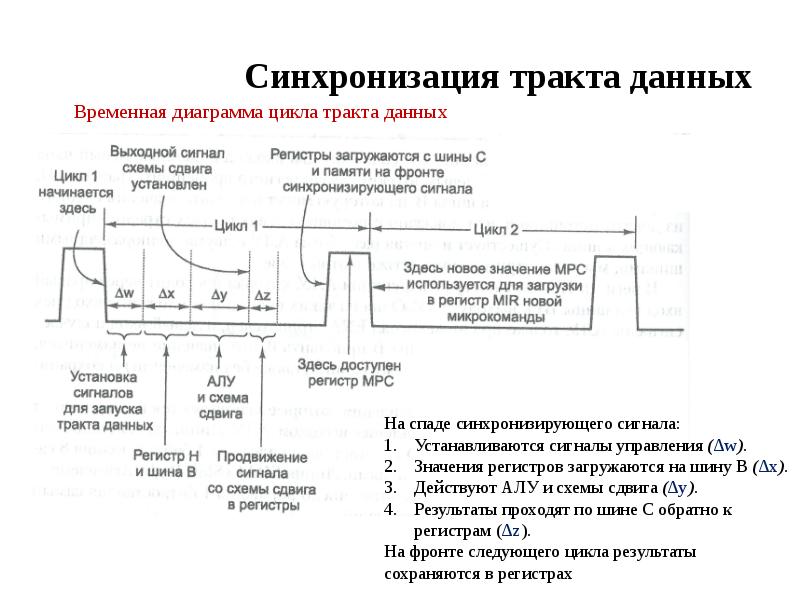

![Синхронизация тракта данных

Операции чтения и записи регистра могут выполняться за один цикл:

Пример: значение SP поместить на шину В, закрыть левый вход АЛУ, установить сигнал INC и сохранить полученный результат в регистре SP увеличив т.о. его значение на 1

Процессы чтения и записи происходят в разных частях цикла:

Когда в качестве правого входа АЛУ выбирается один из регистров, его значение помещается на шину В в начале цикла и хранится там на протяжении всего цикла.

Затем АЛУ выполняет свою работу результат которой через схему сдвига поступает на шину С.

Незадолго до конца цикла, когда значения выходных сигналов АЛУ и схемы сдвига стабилизируются, содержание шины С передается в один или несколько регистров. [Одним из этих регистров вполне может быть тот, с которого поступил сигнал на шину В].](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img9.jpg)

![Синхронизация тракта данных

В начале каждого цикла генерируется короткий импульс

на спаде импульса устанавливаются биты, которые будут запускать все вентили [Δw]

выбирается регистр, и его значение передается на шину В [Δx]

АЛУ и схема сдвига начинают оперировать поступившими к ним данными. После промежутка Δу выходные сигналы АЛУ и схемы сдвига стабилизируются [Δу]

результаты проходят по шине С к регистрам, куда они загружаются на фронте следующего импульса [Δz]

[Загрузка должна запускаться фронтом сигнала и осуществляться мгновенно, так что даже в случае изменений каких-либо входных регистров изменения в шине С будут происходить только после полной загрузки регистров. На фронте импульса регистр, запускающий шину В, приостанавливает свою работу и ждет следующего цикла.]](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img11.jpg)

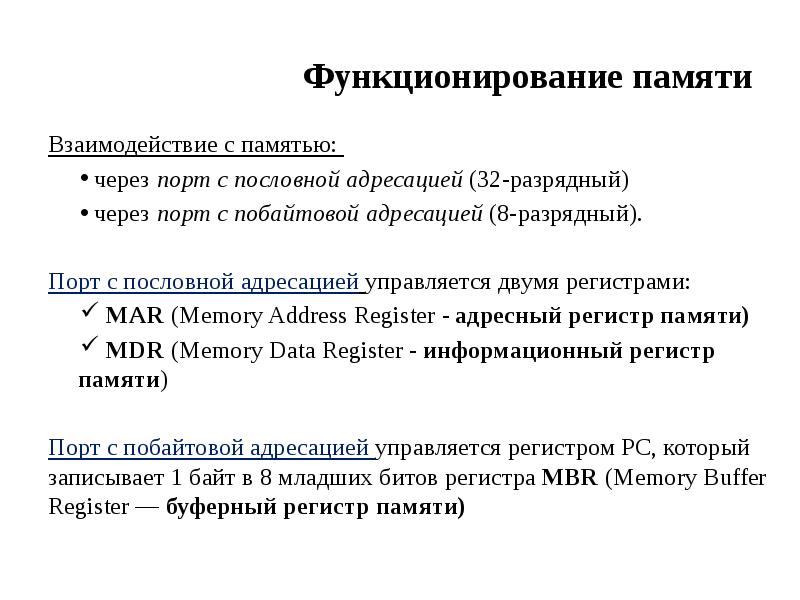

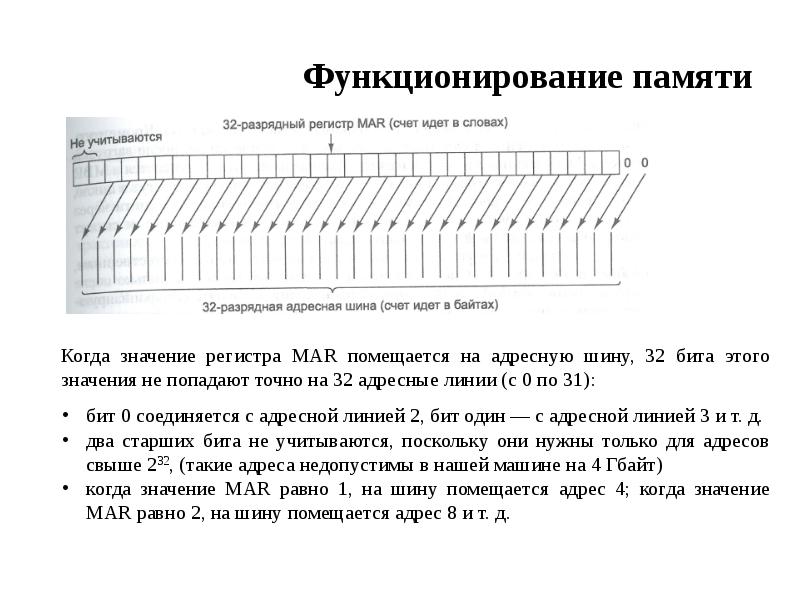

![Функционирование памяти

Регистр MAR содержит адреса слов, таким образом, значения 0, 1, 2 и т. д. указывают на последовательные слова.

Регистр PC содержит адреса байтов, таким образом, значения 0, 1, 2 и т. д. указывают на последовательные байты.

[Если значение 2 поместить в регистр PC и начать процесс чтения, то из памяти считается байт 2, который затем будет записан в 8 младших битов регистра MBR. Если значение 2 поместить в регистр MAR и начать процесс чтения, то из памяти считаются байты с 8 по 11 (то есть слово 2), которые затем будут записаны в регистр MDR]

Регистры MAR и MDR используются для чтения и записи слов данных на уровне архитектуры команд.

Регистры PC и MBR — для считывания программы уровня архитектуры команд, которая состоит из потока байтов.

Во всех остальных регистрах, содержащих адреса, применяется принцип пословной адресации, как и в MAR.](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img14.jpg)

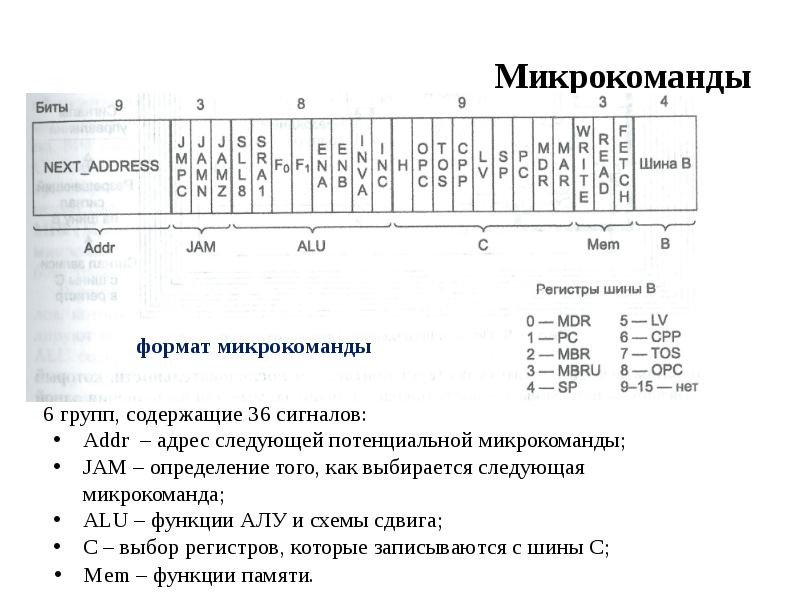

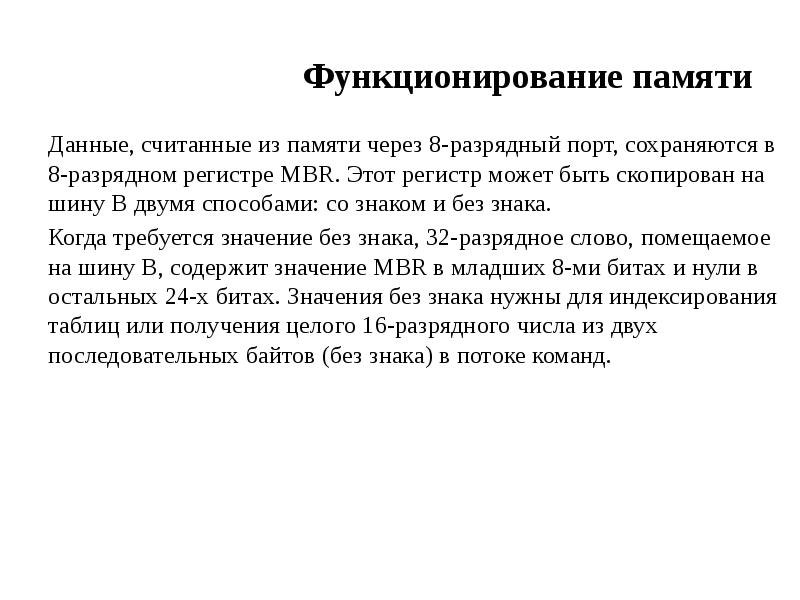

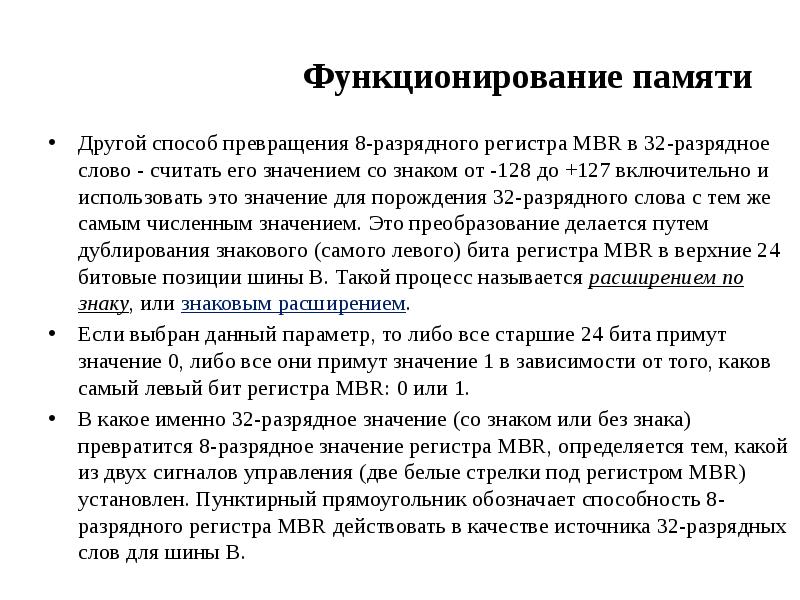

![Микрокоманды

Значения этих 29 сигналов управления определяют операции для одного цикла ТД.

Цикл состоит из передачи значений регистров на шину В прохождения этих сигналов через АЛУ и схему сдвига, передачи полученных результатов на шину С и записи их в нужный регистр(ы).

Если установлен сигнал считывания данных, то в конце цикла после загрузки регистра MAR начинает работать память. Данные из памяти помещаются в MBR или MDR в конце следующего цикла, а использоваться эти данные могут в цикле который идет после него.

[если считывание из памяти через любой из портов начинается в конце цикла k, то полученные данные не смогут использоваться в цикле k + 1 (только в цикле k + 2 и позже)].](/documents_6/ba914ab418af2326eb5ebaa59c3bc368/img20.jpg)